Synopsys VCS工具介绍 |

您所在的位置:网站首页 › VCS user guide官网下载 › Synopsys VCS工具介绍 |

Synopsys VCS工具介绍

|

概述

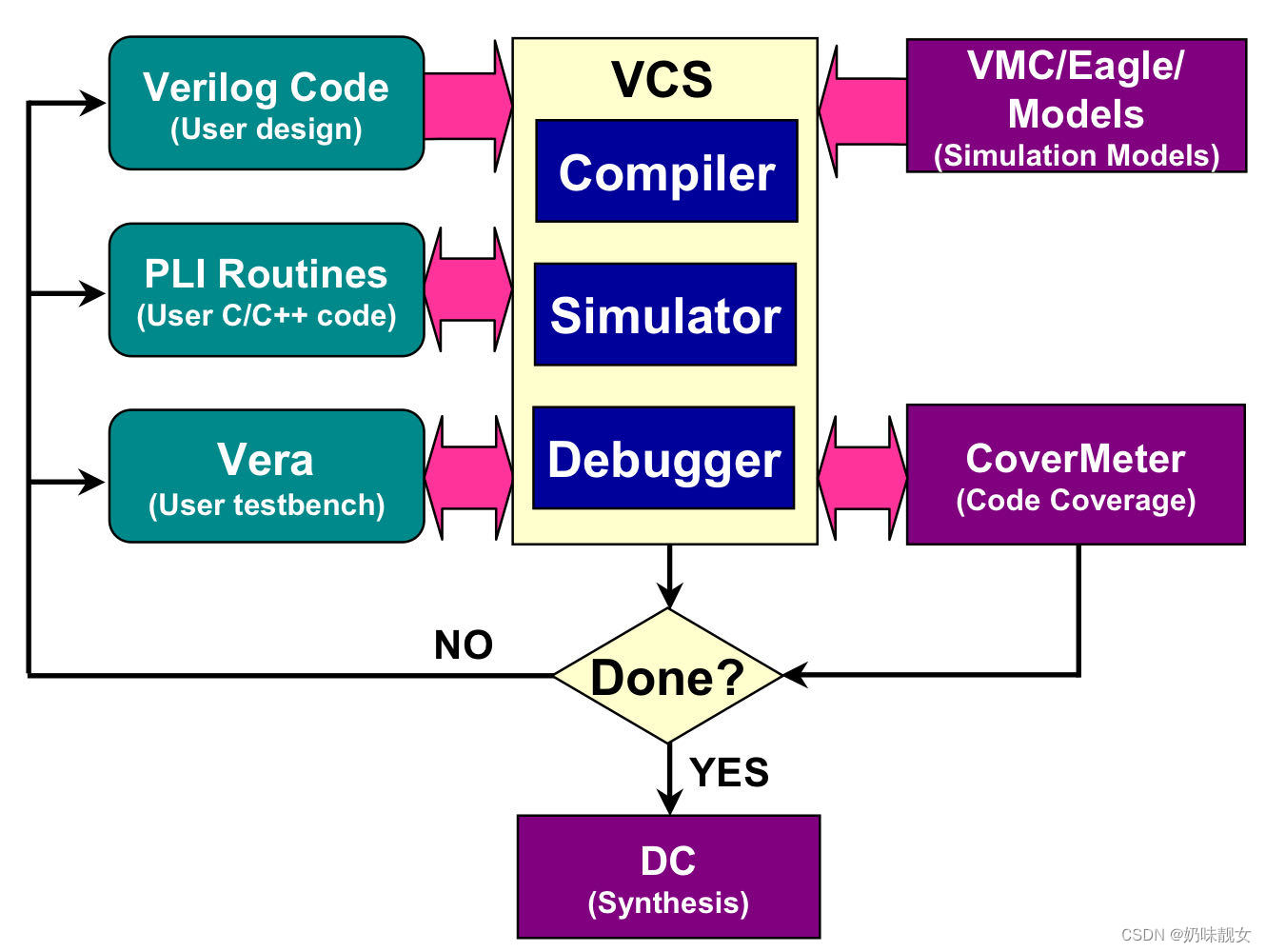

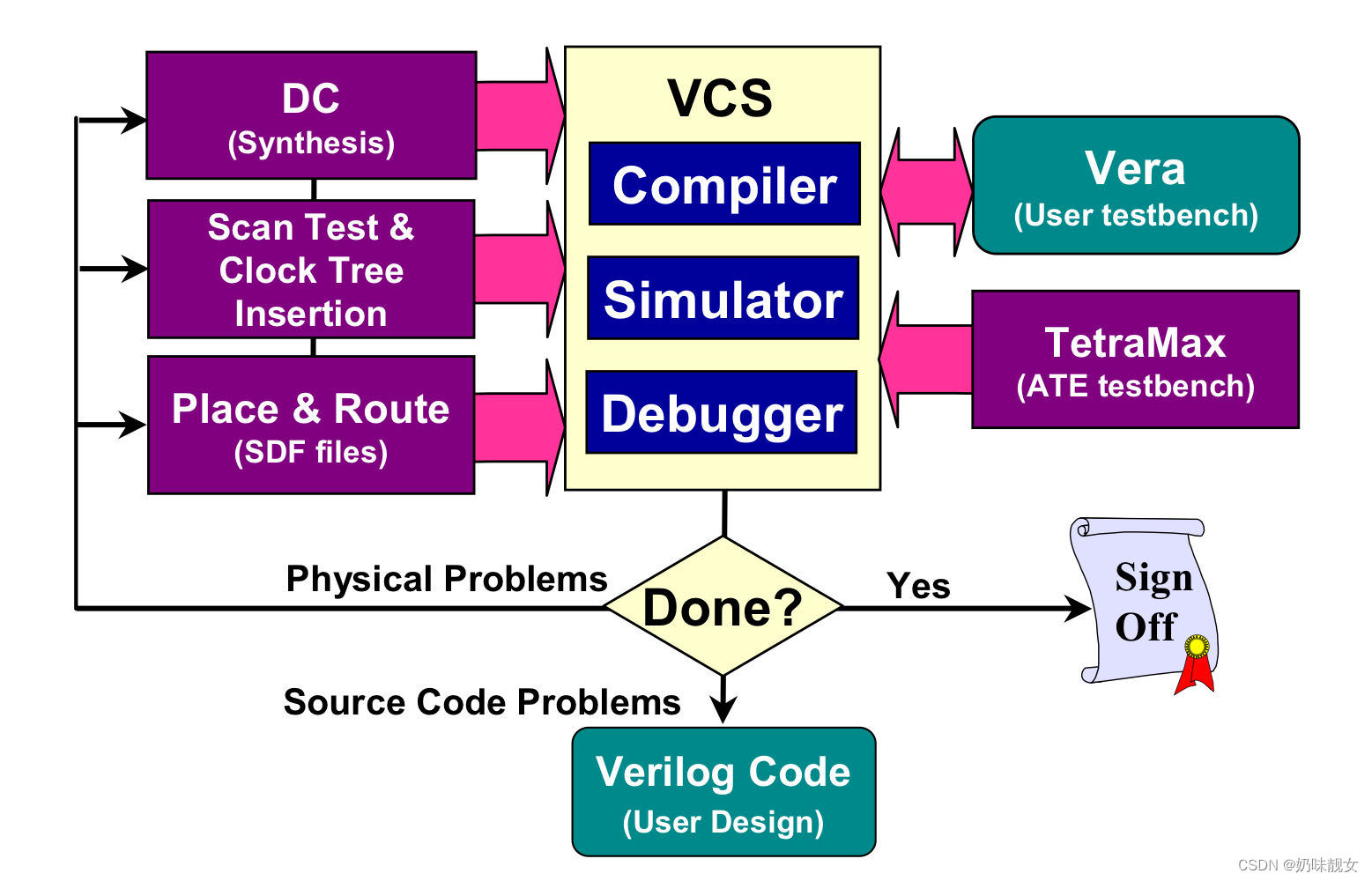

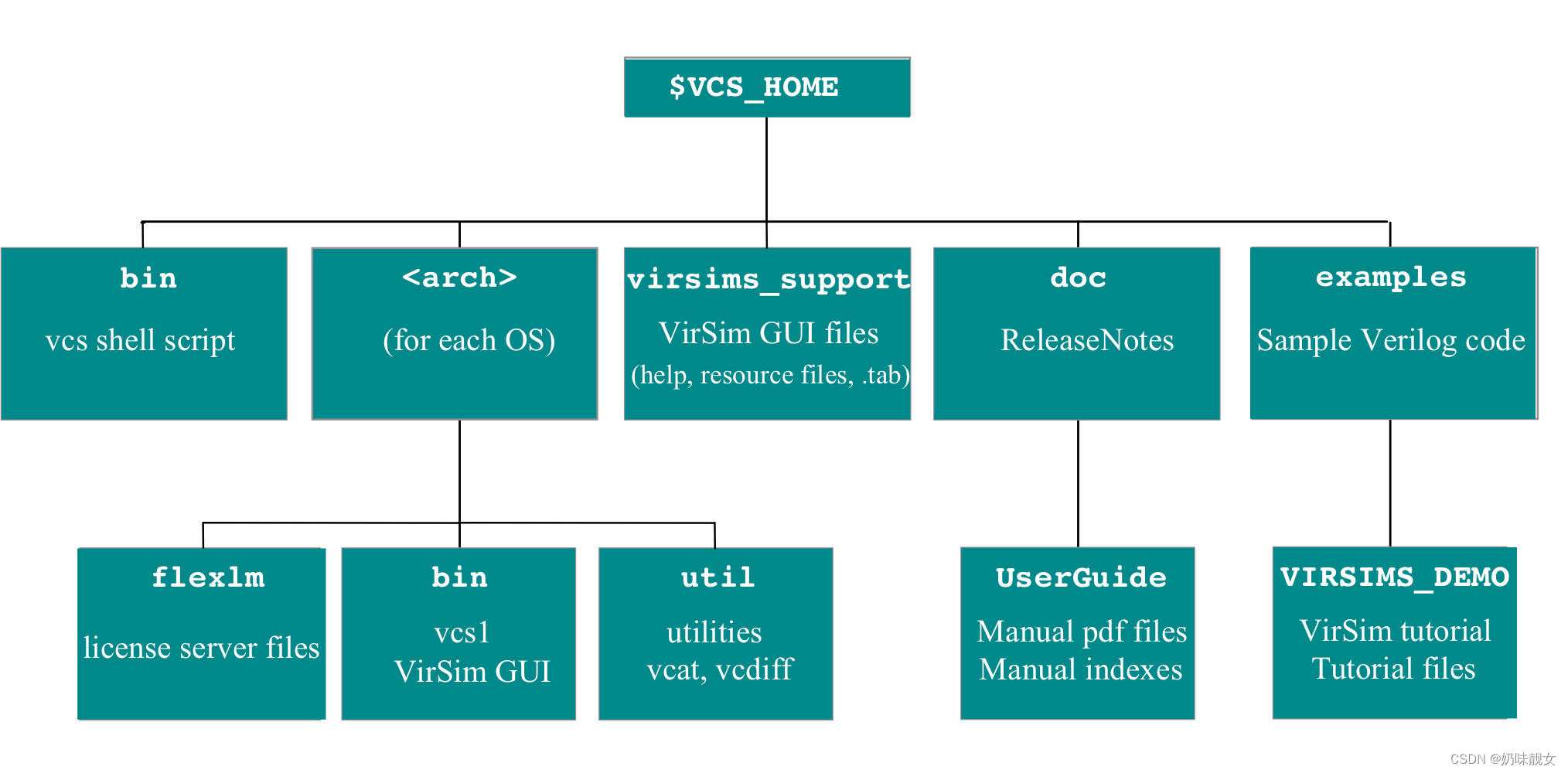

VCS全称为Verilog Compiled Simulator VCS仿真当我们完成了一个模块的设计文件编写后 ,需要 使用VCS进行编译(compile),生成优化的仿真可执行文件对该Verilog设计进行仿真(simulate),执行用户的testbench,报告仿真结果调试(debug)(两种方式) 基于Test:使用CLI(command line interface 命令行界面) 基于GUI(图形用户界面):使用VirSimVCS可支持多种抽象级别的仿真,包括行为级,RTL级,门级(with SDF support)和Sign_off

vcs design.v 解析Verilog源文件,检查是否存在语法错误构建层次结构检查编译选项执行优化(optimization)生成并链接目标代码,run time routines和用户PLI以创建simv仿真二进制可执行文件 运行可执行的simv以进行模拟(simulate)simv exercise design with testbench stimulus(测试台激励)打印 PLI 和 Verilog 系统任务(task)和函数(functions)编译的命令形式 vcs source_files [compile_time_options] source_file:被测模块(DUT design for test)的全部Verilog源文件compile_time_options(可选):控制VCS编译源文件的方式对于优化(optimization)的可见性(visibility)和性能很重要执行后产生仿真二进制可执行文件simv VCS调试(debugger)VCS调试支持: 追踪和定位error三种general method Verilog系统任务调用VCS CLIVCS VirSIm 通过Verilog系统任务进行调试时考虑四个因素 仿真速度信号可视性(由系统任务指定)信号可追踪性可用性/可行性 有助于快速的视觉反馈 可能需要多次迭代插入Verilog系统任务的调用,然后进行编译和模拟常见的Verilog系统任务命令: Debug visibility$display //将格式化信息打印到控制台 $strobe //类似于 $display,但是要等到该时刻所有的操作都执行完后才开始打印 $monitor //监视列表信号,每当列表中的信号发生改变时,打印整个列表中信号的格式化信息 $time //返回当前仿真的时间(64位整数) PS: 用 $display()显示当前变量的值。 用 $strobe()显示用非阻塞赋值的变量值。 用 $monitor()监控和输出参数列表中的表达式或变量值。 Stopping simulation$stop //暂停仿真 $finish //退出仿真 Simulation stimulus and reference$readmemh //read ASIC data from a disk file(16进制) $readmemb //read ASIC data from a disk file(2进制) 基于CLI的调试编译并唤醒CLI debugger 方法一: vcs source.v +cli+3 -R -s //-s 唤醒CLI并在0时刻终止仿真 方法二: vcs source.v +cli+3 simv source.v -s //+cli+1 可读取nets和寄存器并写入寄存器(或写作+cli 或 -I) //+cli+2 enable callback(e.g. break@var) //+cli+3 Enable force and release of nets not including registers //+cli+4 Enable force and release of nets including registers -line //Enable source code single stepping capability(编译时间选择) //+cli+2 增加10%的运行时间,+cli+3 增加50% //-line 增加的运行时间远大于100% //为了加快仿真速度,请本地化CLI scope vcs +cli+modA=2 +cli+modB=3 source.v 基于VirSim的交互模式的调试流程概述: 使用VirSim交互模式唤醒VirSim GUI以编译Verilog设计通过交互界面设置仿真time step(步长),在Source窗口和波形窗口设置breakpoint来进行仿真在波形窗口(Waveform)、寄存器窗口(Register)、逻辑窗口(Logic)和源代码窗口(Source)检查仿真结果,并定位代码中的错误零碎补充 VCD文件:全称为Verilog Change Dump文件(dump:转储), VCD+文件:类似于VCD文件,储存了转换时间,网络(nets)和寄存器的值,以及设计的层次结构(hierarchy)。相比于二进制文件,需要更少的磁盘空间,加载更快,支持记录源代码的执行顺序。内置VCD+系统任务,用于控制VCD+文件的内容和大小。VCD文件可以转换为VCD+文件 VCD+系统任务举例:$vcdpluson 、 $vcdplusoff 、 $vcdplustraceon 、 $vcdplustraceoff 、 $vcdplusautoflushon 、 $vcdplusautoflushoff 、 $vcdplusflush 、 $vcdplusdeltacycleon 、 $vcdplusdeltacycle 、 $vcdplusglichon 、 $vcdplusglichoff 、 $vcdplusevevt PLI:Programming Language Interface,C程序和Verilog仿真器之间的接口,支持用户自定义任务或函数 规范编码 避免在时序逻辑中使用repeat, wait, fork_jion, assign_deassign, force_release, disable, case 避免在他task中使用延时,task声明时不要有延时(如 #10 task_sync(s);) 避免在非阻塞赋值中使用延时(如 q |

【本文地址】

今日新闻 |

点击排行 |

|

推荐新闻 |

图片新闻 |

|

专题文章 |